CMOS

Komplementarni metal-oksid-poluprovodnik (engl. Complementary metal–oxide–semiconductor, CMOS) se koristi za izradu integrisanih kola. CMOS tehnologija se koristi kod mikroprocesora, mikrokonterolera, statične RAM memorije i drugih digitalnih logičkih kola. CMOS tehnologija se takođe koristi za nekoliko analognih kola kao što su |slike senzore (CMOS senzor), konnvertori podataka i visoko integrisani radio-primopredajnici za više vrsta komunikacija. Frank Vanlas patentirao je CMOS 1963. godine.

CMOS se, takođe, ponekad odnosi i na „komplementarno-simetrični“ metal-oksid poluprovodnik (ili COS-MOS).[1] Fraza „komplementarno-simetriični“ odnosi se na činjenicu da tipičan digitalni stil dizajniranja CMOS koristi komplementarne i simetrične parove p tipa i p tipa metal oksid poluprovodnika (MOSFET) za logičke funkcije.[2]

Dve važne karakteristike CMOS uređaja jesu visok imunitet buke i mala statička potrošnja energije. Budući da je jedan tranzistor u paru uvek isključen, serije kombinacija crpi značajnu energiju, ali samo momentalno tokom prebacivanja iz uključenog u isključeno stanje. Shodno tome, CMOS uređaji ne proizvode mnoge bespotrebne toplote kao neke druge logičke forme, na primer, tranzistor-tranzistor logika (TTL) ili NMOS (N-tip MOS) logika, koji obično imaju neke trajne struje, čak i kada se ne menja stanje. CMOS takođe omogućava visoku gustinu logičkih funkcija na čipu. To je bio glavni razlog da CMOS postane najčešće korišćena tehnologija za implementaciju u VLSI čipovima.

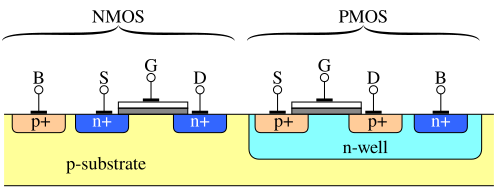

Fraza "metal-oksid-poluprovodnik" odnosi se na fizičku strukturu određenih terensko-efektivnih tranzistora, koji imaju elektrodu sa matalnim vratim postavljenu na oksidni izolator, koji je na vrhu poluprovodničkog materijala. Nekada se koristio aluminijum, ali danas se koristi polisilikon. Druga metalna vrata su napravila preokret sa pojavom visokih-k dielektričnih materijala u CMOS procesu, a objavio su ih IBM i Intel za 45 nanometar čvor i šire.

"CMOS" se odnosi i na poseban stil dizajna digitalnih kola i na familije procesa koje se koriste za implementaciju kola na integrisanim kolima (čipovima). CMOS kolo rasipa manje energije od logičkih familija otpornih na opterećenje. Od kada se ova prednost povećala i postala važnija, CMOS procesi i varijante su počele da dominiraju, tako da se velika većina savremenih integrisanih kola proizvodi na CMOS procesima.[3] Od 2010. godine, CPUs je sa najboljim performansama po vatu svake godine, imao CMOS statičku logiku od 1976. godine.

CMOS kola koriste kombinaciju p kanala i n kanala matal-oksid poluprovodničkih terensko efektivnih tranzistora (MOSFETs) za implementaciju logičkih vrata. Iako CMOS ligika može da se implementira sa diskretnim uređajima za demonstracije, komercijalni CMOS proizvodi su integrisana kola sastavljena od, do milion tranzistora oba tipa na pravougaonoj ploči silicijuma, površine između 10 i 400 mm2.

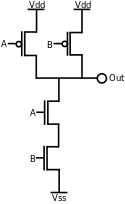

CMOS kola su konstruisana na takav način da svi PMOS (P-tip MOS) tranzistori moraju da imaju ili ulaz iz napajanja ili iz drugog PMOS tranzistora. Slično, svi NMOS tranzistori moraju imati ulaz ili iz zemlje ili od drugog NMOS tranzistora. Sastav PSMO tranzistora stvara mali otpor između njegovog izvora i kontaktnih odvoda kada su primenjena nisko naponska vrata i velika otpornost kada su primenjena visoko naponska vrata. Sa druge strane, sastav NMOS tranzistora stvara veliki otpor između izvora i odvoda kada su primenjena nisko naponska vrata i mali otpor kada su primenjena visoko naponska vrata. CMOS ostvaruje redukciju struje dopunjujući svaki nMOSFET sa pMOSFET i spajajući oba vrata i oba odvoda. Visoki napon na vratima uzrokuje da nMOSFET provodi a pMOSFET ne porvodi, dok niski napon na vratima radi suprotno. Ovo uređenje u velikoj meri smanjuje potrošnju energije i stvaranje toplote. Međutim, tokom prebacivanja oba MOSFET-a kratko provode kako napon na vratima ide sa jednog u drugo stanje. Ovo stavara kratak prekid u napajanju i postaje ozbiljan problem na visokim frekvencijama.

Slika desno pokazuje šta se dešava kada je ulaz povezan sa PMOS tranzistorom (vrh dijagrama) i NMOS tranzistorom (donji deo dijagrama). Kada je napon na ulazu A nizak, NMOS tranzistorski kanal je u stanju velike otpornosti. Ovo ograničava struju koja može da teče od Q do zemlje. PMOS tranzistorski kanal je u stanju male otpornosti i mnogo više struje može da protekne od napajanja do izlaza. Pošto je otpornost između napona napajanja i Q niska, pad napona između izvora napajnja i Q , zbog stuje koja dolazi iz Q, je mali. Izlaz zbog toga registruje visok napon.

S druge stane, kada je napon na ulazu u A visok, PMOS tranzistor je u OFF (visoka otpornost) stanju kako bi se ograničilo proticanje struje od pozitivnog izvora do izlaza, dok je NMOS tranzistor u ON (mala otpornost) stanju, što omogućava izlaz iz odvoda do zemlje. Pošto je otpornost između Q i zemlje mala, pad napona potiče zbog struje koja biva uvučena u Q, stavljanjem Q malo iznad zemlje. Mali pad je rezultat niskog napona na izlazu.

Ukratko, izlazi PMOS i NMOS tranzistora su komplentarni na taj način da kad je nizak ulaz, izlaz je visok, i kada je ulaz visok izlaz je nizak. Zbog ovakvog ponašanja izlaza i ulaza, izlaz CMOS kola je inverzan od ulaza.

Napajanja za CMOS se zovu VDD i VSS, ili VCC i zemlja (Ground-GND), u zavisnosti od proizvođača. VDD i VSS su prenosioci od konvencijalnog MOS kola i održavaju odvod i izvorno snabdevanje.[4] Ono se ne odnosi direktno na CMOS jer su oba snabdevanja realni izvori snabdevanja. VCC i GND su preneseni od TTL logike i ta nomenklatura je bila zadržana uvođenjem 54C/74C linije CMOS.

Važna karakteristika CMOS kola je dualnost koja postoji između njegovih PMOS tranzistora i CMOS tranzistora. CMOS kolo je napravljeno tako da uvek omogući postojanje puta od izlaza do ili napajanja ili zemlje. Da bi se ovo postiglo, skup svih puteva na izvor napona mora da bude komplement skupa svkih puteva na zemlji. Ovo se lako postiže definisanjem izraza NE od strane drugog. Zbog De Morganovih zakona bazne logike, PMOS paralelni tranzistori imaju odgovarajuće NMOS redne tranzistore, dok PMOS redni tranzostori imaju odgovarajuće NMOS paralelne tranzistore.

Kompleksnije logičke funkcije, kao one koje uključuju vrata I i ILI, zahtevaju manipulisanje putevima između vrata pri prezentaciji logike. Kada se put sastoji od dva redna tranzistora, oba tranzistora moraju imati mali otpor za odgovarajući mrežni napon, modelovanje I. Kada se put sastoji od dva paralelna tranzistora, ili jedan ili oba tranzistora moraju da imaju mali otpor da bi povezali izvor mrežnog napona sa izlazom, modelovanje ILI.

Na desnoj starni je prikazan je dijagram kola sa vratima NI u CMOS logici. Ako su oba, A i V ulaza, visoka, onda će oba NMOS tranzistora (donja polovina dijagrama) provoditi, nijedan od PMOS tranzistora (polovina gore) neće provoditi, i biće uspostavljen provodni put između izlaza i Vss (zemlje), stvarajući niski izlaz. Ako su ili A ili B niski ulazi, jedan od NMOS tranzistora neće provoditi, jedan od PMOS tranzistora hoće i biće uspostavljen provodni put između izlaza i Vdd (mrežnog napona), stvarajući visoki izlaz.

Prednost CMOS nad NMOS je u tome što su oba izlazna tranzistora, nisko-ka-visokom i visoko-ka-niskom, brza, pošto pull-up tranzistori imaju malu otpornost kada se uključe, za razliku od opterećenih otpornika u NMOS logici. Dodatno, izlazni signal vrti pun napon između niskih i visokih šina. Ovaj snažan, više skoro simetričan odgovor, takođe pravi CMOS koji je otporniji na šum.

Vidi Logical effort za motod izračunavanja kašnjenja u CMOS kolu.

Primer pokazuje NI logički uređaj nacrtan kao fizička reprezentacija njegove proizvednje. Data je perspektiva fizičkog izgleda, „ptičija perspektiva“, naslaganih slojeva. Kolo je konstruisano od p tipa podloge. Polisilikon, difuzuja, i n–well (n-rupa) se odnose na "bazni sloj", i u stvari, oni su umetnuti u rovove p tipa podloge. Kontakti uspustavljaju vezu prodiranjem kroz izolacione slojeve između baznih slojeva i prvog metalnog sloja (metal 1).

Ulazi u NI (predstavljeni zelenom bojom) su u polisilikonu. CMOS tranzistori (uređaji) se formiraju ukrštanjem polisilikona i difuzije; N difuzija za N uređaj i R difuzija za R uređaj (ilustrovano u boji lososa i u žutoj boji, respektivno). Izlaz ("out") je spojen sa metalom (ilustrovan cijan bojom). Spojevi između metala i polisilikona ili difuzije realizuju se pomoću kontakta (ilustrovani crnim kvadratima). Fizički izgled primera odgovara NI logičkom kolu datom u prethodnom primeru.

N uređaj se proizvodi na podlozi R tipa, dok se R uređaj proizvodi na N tipu i n–well. „Dodirnuta“ podloga R tipa je je povezana sa VSS i dodirnuti N-type n-well je povezan sa VDD, da bi se sprečilo gornje zatvaranje.

.

CMOS logika rasipa manje energije nego NMOS logička kola zato što CMOS rasipa energiju samo kada se prebacuje ("dinamička energija"). Na tipičnom ASIC u modernom 90 nanometarskom procesu, prebacivanje izlaza može trajati 120 pikosekundi, a dešava se svakih 10 nanosekundi. NMOS logika rasipa energiju uvek kada je tranzistor uključen, zato što postoji strujni put od Vdd to Vss kroz opterećeni otpornik i mrežu n-tipa.

Statična CMOS vrata su veoma energetski efikasna zato što je rasipanje energije svedeno gotovo na nulu u stanju mirovanja. Ranije, na potrošnju energije CMOS uređaja nije se vodilo mnogo računa prilikom dizajna čipova. Faktori kao što su brzina i površina su važani faktori tokom dizajna. Dok se CMOS tehnologija kretala ispod sub-mikronskog nivoa, potrošnja energije po jedinici površine čipa se izuzetno povećala.

Uopšteno klasifikovano, rasipanje energije u CMOS kolu se javlja usled postojanja dve komponente:

- Statičko rasipanje

- Pod-prag provodljivosti kad je tranzistor isključen

NMOS i PMOS tranzistori imaju vrata-izvor naponski prag, ipod kojeg struja (zove se pod-prag struja) kroz uređaj opada eksponencijalno. Istorijski, CMOS dizajn radi pri mrežnom naponu mnogo većem od njegovog naponskog praga (Vdd može da bude 5 V, a Vth za NMOS i PMOS može da bude 700 mV). Specijalni tip CMOS tranzistora sa skoro nula mrežnim naponskim pragom je prirodan tranzistor.

- Tunelovanje struje koz oksidna vrata

SiO2 je veoma dobar izolator, ali sa malom debljinom nivoa elektroni mogu da budu tunelovani kroz veoma tanak izolator; verovatnoća opada eksponencijalno sa debljinom oksida. Tunelovanje struje postaje veoma važno za tranzistore tehnologije ispod 130 nm sa oksidnim vratima od 20 Å ili tanjim.

- Curenje struje kroz obrnute bias diode

Javlja se malo suprotno curenje zbog formiranja obrnutog biasa između dufuzionih regiona i rupe (jame) (npr. p-tip difuzije i n-rupa), rupe i podloga (npr. n-rupa i p-podloga). U savremenom procesu curenje diode je veoma malo u odnosu na pod prag i tunelovanje struje, tako da to može da se zanemari tokom energetskih izračunavanja. (Napon na ulazu (ili baza) nekog tranzistora ili vakuum cevi, uslovljavaju rad uređaja u provodnim stanju. Kada se primenjuje kontrolni napon (ulazni napon) do vrata, dodaje se bias, koji omogućava da rezultantni napon bude veći ili manji, na osnovu zbira dva.)

- Struja kao posledica događaja (sontention) u srazmernim kolima

- Dinamičko rasipanje

- Punjenje i pražnjenje kapacitivnog opterećenja

CMOS kola rasipaju energiju punjenjem raznih kapacitativnih opterećenja (uglavnom kapacitativnost vrata i žice, ali takoće i kapacitativnost odvoda i nekih izvora) kad god se zamenjuju. U jednom kompletnom ciklusu CMOS logike, struja protiče od VDD do kapacitativnog opterećenja da bi ga napunila, a potom teče od napunjenog kapacitativnog opterećenja do zemlje tokom pražnjenja. Zato tokom jednog ciklusa punjenja/pražnjenja, ukupno Q=CLVDD je takvo da se prenosi od VDD do zemlje. Množi se sa promenom frekvencije na kapaciattivnom opterećenju da bi se dobila upotrebljena struja, i množi se opet sa naponom da bi se dobile karakteristike zamenjene rasute energije od strane CMOS uređaja:

Pošto većina vrata ne rade/prebacuju u svakom vremenskom cilusu, one su često praćene faktorom, koji se zove aktivni faktor. Sada, dinamično rasipanje energije može biti ponovo napisano kao .

Sat u sistemu ima aktivni faktor α=1, pošto on raste i pada u svakom ciklusu. Najviše podataka ima aktivni faktor od 0,1.[5] Ako se ispravno kapacitativno opterećenje proceni na čvoru zajedno sa njegovim aktivnim faktorom, dinamičko rasipanje energije na tom čvoru može efikasno da se izračuna.

- Rasipanje snage kratkih kola

Pošto postoji konačan porast/pad vremena i za pMOS i cMOS, za vreme prenosa, na primer, iz isključenog u uključeno, oba tranzistora će biti uključena za kratak vremenski period u kome će struja pronaći put direktno od VDD do zemlje, stvarajući kratki spoj. Kratko rasipanje energije kola povećava se porastom i smanjenjem vremena tranzistora.

Dodatni oblik potrošnje energije postaje značajan 1990. godine pošto žice na čipu postaju uže i duže žice praveći veći otpor. CMOS vrata na krajevima tih otpornih žica vide spore ulazne tranzicije. U sredini ovih promena, i NMOS i PMOS logičke mreže su delimično provodne, i struja teče direktno od Vdd do VSS. Energija koja se tako koristi naziva se crowbar energija. Pažljivi dizain, koji izbegava slabe izbačene dugačke tanke žice, je poboljšao ovaj efekat, a crowbar energija je skoro uvek značajno manja nego energija zamene.

Da bi ubrzali dizain, proizvođači su se okrenuli ka konstrukcijama koje imaju niže naponske pragove, ali i zato što moderni NMOS tranzistor, sa Vth od 200 mV, ima značajan podprag curenja struje. Dizajni (npr. desktop procesora) koji uključuju ogroman broj kola koja se aktivno ne menjaju, još uvek troše energiju zbog curenja struje. Curenje energije je značajan deo ukupne potrošene energije sa takvim dizajnom. Viši prag CMOS (Multi-threshold CMOS - MTCMOS), sada dostupan livnicama, je jedan od pristupa upravljanja cerenjem energije. Sa MTCMOS, visoki Vth tranzistori se koriste kada brzina zamene nije kritična, dok se niski Vth tranzistori koriste za osetljive puteve brzine. Dalji tehnološki napretci, koji koriste čak i tanja dielektrična vrata, imaju dodatnu komponentu curenja zbog tunelovanja struje kroz izuzetno tanka dielektrična vrata. Korišćenjem visoke k-dielektrike, umesto slicijum dioksida, dobijaju se konvencionalna dielektrična vrata, koja dozvoljavaju slične perfomanse uređaja ali sa debljim izolatorom vrata, čime se izbegava curenje. Smanjenje u curenju energije korišćenjem novog materijala i sistema dizajna je važan za održavanje kvaliteta CMOS.[6]

Pored digitalnih aplikacija, CMOS tehnologija se takođe koristi u analognim aplikacijama. Na primer, postoji CMOS operacioni pojačavač integrisanih kola (ICs), koji je dostupan na tržištu. Transmisiona vrata mogu da se koriste umesto relejnih signala. CMOS tehnologija se takođe široko koristi za radio frekvetna (RF) kola sve do mikrotalasnih peći, u mešovitim signalnim (analogni + digitalni) aplikacijama.

Konvencionalni CMOS uređaji rade u rasponu od -55 °C do +125 °C. Bilo je teoretskih indikacija avgusta 2008. godine da će silikonski CMOS raditi na -233 °C (40 K). Funkcionisanje na temperaturama blizu 40K je do sada postignuto korišćenjem overklokovanim AMD Phenom II procesorom sa kombinacijom tečnog azota i tečnog helijuma za hlađenje.[7]

Ultra mali (L=20 nm, W=20 nm) CMOS tranzistori postižu jednoelektronski limit kada rade na veoma niskim temperaturama, u rasponu od -269 °C (4 K) do -258 °C (15 K). Tranzistor pokazuje Coulomb blokadu zbog progresivnog punjenja jednim po jednim elektronom. Broj elektrona zatvoren u kanalu se prenosi usled napona na vratima, startujući punjenje od nula elektrona, a onda može da se javi skup od jednog ili više elektrona.[8]

- ↑ COS-MOS was an RCA trademark, which forced other manufacturers to find another name — CMOS

- ↑ „What is CMOS Memory?”. Wicked Sago. Pristupljeno 3. 3. 2013.

- ↑ Baker, R. Jacob (2008). CMOS: circuit design, layout, and simulation (Second izd.). Wiley-IEEE. str. xxix. ISBN 978-0-470-22941-5.

- ↑ „CMOS, the Ideal Logic Family”. Arhivirano iz originala na datum 09. 12. 2011. Pristupljeno 28. 10. 2013.

- ↑ K. Moiseev, A. Kolodny and S. Wimer, "Timing-aware power-optimal ordering of signals", ACM Transactions on Design Automation of Electronic Systems, Volume 13 Issue 4, September 2008, Association for Computing Machinery (ACM)

- ↑ A good overview of leakage and reduction methods are explained in the book Leakage in Nanometer CMOS Technologies. ISBN 978-0-387-25737-2.

- ↑ Moorhead, Patrick (15. 1. 2009.). „Breaking Records with Dragons and Helium in the Las Vegas Desert”. blogs.amd.com/patmoorhead. Arhivirano iz originala na datum 07. 07. 2012. Pristupljeno 18. 9. 2009.

- ↑ Prati, E.; De Michielis, M.; Belli, M.; Cocco, S.; Fanciulli, M.; Kotekar-Patil, D.; Ruoff, M.; Kern, D. P. i dr.. (2012). „Few electron limit of n-type metal oxide semiconductor single electron transistors”. Nanotechnology 23 (21): 215204. DOI:10.1088/0957-4484/23/21/215204. PMID 22552118.

- Baker, R. Jacob (2008). CMOS: circuit design, layout, and simulation (Second izd.). Wiley-IEEE. str. xxix. ISBN 978-0-470-22941-5.

- Baker, R. Jacob (2010). CMOS: Circuit Design, Layout, and Simulation, Third Edition. Wiley-IEEE. str. 1174. ISBN 978-0-470-88132-3. http://CMOSedu.com

- Weste, Neil H. E.; Harris, David M. (2010). CMOS VLSI Design: A Circuits and Systems Perspective, Fourth Edition. Boston: Pearson/Addison-Wesley. str. 840. ISBN 978-0-321-54774-3. http://CMOSVLSI.com/

- Veendrick, Harry J. M. (2008). Nanometer CMOS ICs, from Basics to ASICs. New York: Springer. str. 770. ISBN 978-1-4020-8332-7.

- Carver Mead and Lynn Conway (1980). Introduction to VLSI systems. Boston: Addison-Wesley. ISBN 978-0-201-04358-7.

- Raspored pinova za razne porodice integralnih kola

- CMOS gate description and interactive illustrations

- LASI is a "general purpose" IC layout CAD tool. It is a free download and can be used as a layout tool for CMOS circuits.